Il variatore è diventato asincrono

-

⁇

-

In: Olof Kindgren

-

-

-

Ci sono molti framework di convalida oggi che consentono agli utenti di scrivere i propri test su qualsiasi cosa, da C++ a Python. Ma per chiunque si attenga a Verilog e abbia installato l’ambiente UVM, ci sono ancora opportunità di miglioramento.

C’è un grande interesse nel campo dell’utilizzo del simulatore Verilock più veloce del mondo, il Verilator, in combinazione con UVM come open source.

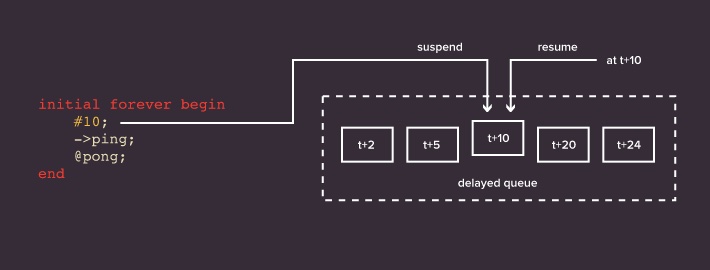

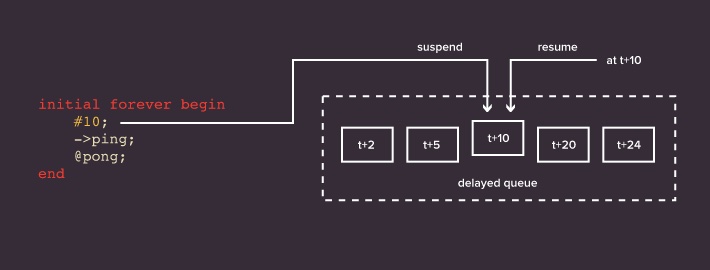

In precedenza, Verilater gestiva solo gli eventi di sincronizzazione dell’orologio completi, ma di recente il supporto per la pianificazione dinamica ha compiuto un passo importante in quella direzione quando supporta ritardi di segnale simulati ed eventi asincroni.

“Pluripremiato esperto del web. Incurabile fanatico della cultura pop. Evangelista estremo del cibo. Specialista televisivo. Pioniere della birra.”